Zurich, October 22, 2020

Tetra Semiconductors Ltd. proudly announces their 4-channel CDR chip TSC2PAM designed to replace DSPs in existing 8-channel 400Gb Ethernet optical modules. While matching all RF performance requirements of Ethernet modules, Tetra’s new CDR offers a significantly lower power consumption and BOM costs at much smaller size than DSPs. Thus, the TSC2PAM opens the door to 400Gb Ethernet modules with lower costs and power consumption per bit than the currently widely deployed 100G Ethernet solutions. With Tetra’s analog CDR technology, module manufacturers now have access to a low risk solution to optimize their existing or new modules with minimal design-in effort.

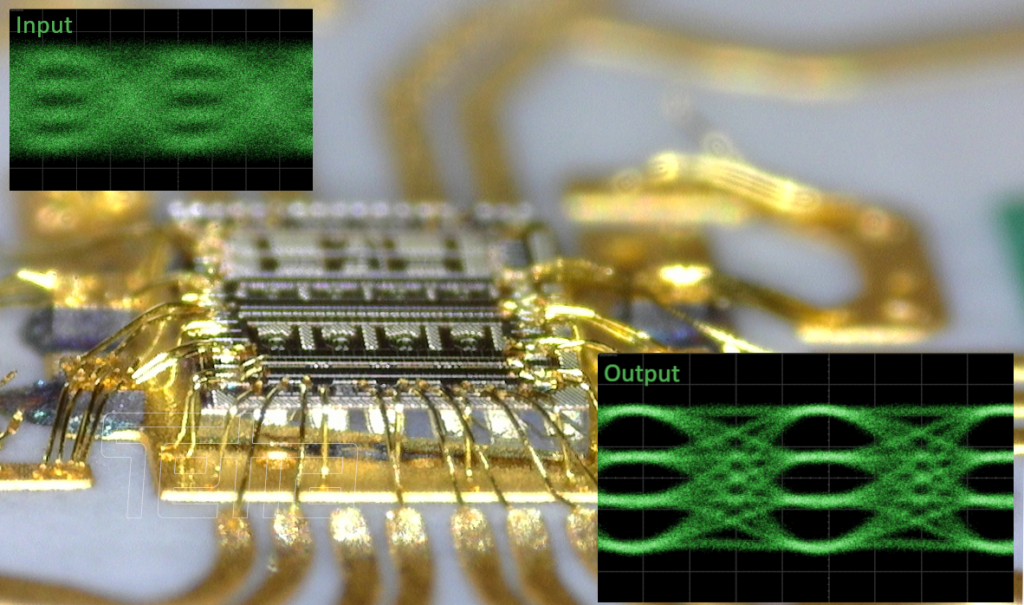

Tetra Semiconductors’ TSC2PAM 26.5 Gbaud 4-channel CDR includes a high-performance adaptive CTLE and DFE equalization stage. Acquiring time for optimal equalization stage settings is less than 100 ms. The figure below shows the error free recovery of a degraded input signal generated with a 190cm (72″) lossy RF cable without the use of forward error correction.

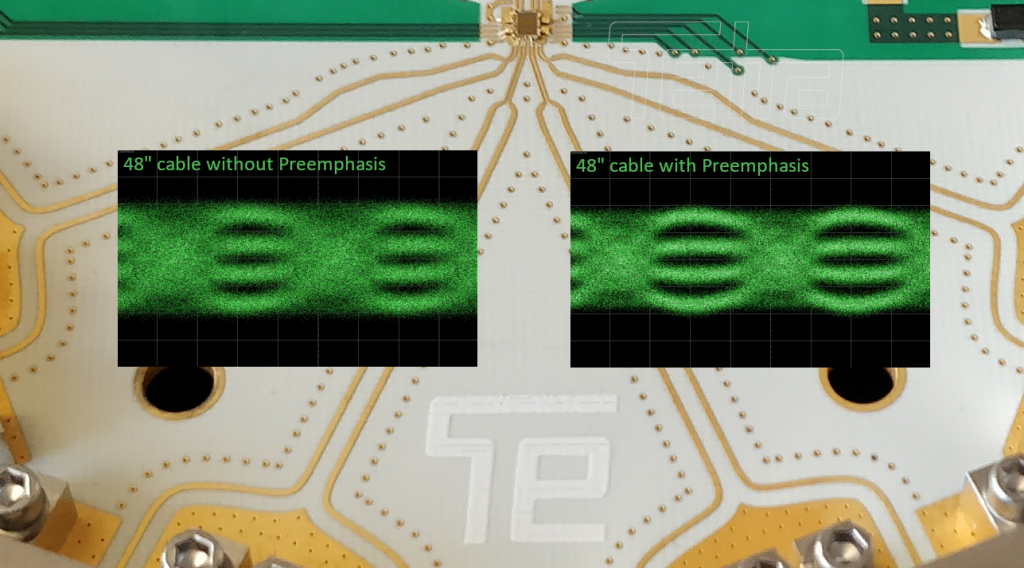

The TSC2PAM input stage provides a superior input sensitivity combined with a large dynamic range and contains an automated acquisition circuit for detecting the input thresholds. The fast CML-based output stage of the chip accommodates a digitally controllable output swing (up to 1.1 Vpp differential) with pre- and post-cursor equalization to precondition the signal for potential losses of the transmission path.

Tetra Semi’s patented CDR of the TSC2PAM recovers any PAM4 or NRZ signal within the range of 24GHz to 29GHz. TSC2PAM uses the same very low latency architecture (only 2 clock cycles) as in the TS1 chipset. Tetra’s TS1 chipset operates reliably up to 58 Gbaud (PAM4) demonstrating the scalability of the current architecture.

In summary, the TSC2PAM provides:

- high gain adaptive input CTLE and DFE equalization

- very low overall chip latency of only two clock cycles

- reliable CDR with very fast acquisition time (<100ms)

- excellent output eye quality with selectable output swing up to 1.1 Vpp

- pre- and post-cursor equalization at the output

- cost-efficient 400G Ethernet solution thanks to low power (450mW per channel) and small form factor (1.5 mm x 1.7 mm)

- selectable CDR loop bandwidth and gain

The chips are available as bare die or a 5mmx5mm QFN-type packaged.

For further information please visit www.tetra-semi.com or contact us at: info@tetra-semi.com.