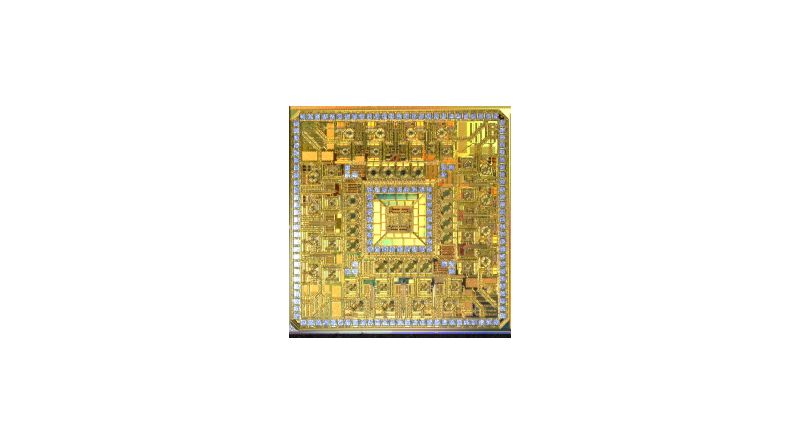

TS4 Chipset

| Part No. | Product Type | Description | Market Segment | Availability |

|---|---|---|---|---|

| TSR4PAM | 4 channel 106 Gbit/s PAM Receiver | The TSR4PAM includes a TIA at the input to convert currents coming from a Photo Diode into a differential signal followed by a CDR Retimer with a 50 Ohm Output. The chip can operate at input bit rates of up to 106 Gbit/s. It can be operated in a low Power linear bypass mode, or in re-timed mode for better link margin. | 400/800G Ethernet | available |

| TST4PAM | 4 channel 106 Gbit/s PAM Transmitter | The TST4PAM includes a VCSEL driver at the output and a CDR Retimer with a 50 Ohm Input. The chip can operate at input bit rates of up to 112 Gbit/s. It can be operated in a low Power linear bypass mode, or in re-timed mode for better link margin. | 400/800G Ethernet | available |

| TSC4PAM | 4 channel 106 Gbit/s PAM Transmitter | The TSC4PAM includes a Modulator driver at the output and a CDR Retimer with a 50 Ohm Input. The chip can operate at input bit rates of up to 112 Gbit/s. It can be operated in a low Power linear bypass mode, or in re-timed mode for better link margin. | 400/800G Ethernet | available |

Related News:

Tetra Semiconductors Achieves Milestone with Industrialization of Advanced PAM4 Chipsets

Zurich, Switzerland — June 6, 2025 Tetra Semiconductors , a leader in the semiconductor industry specializing in analog integrated circuits

Tetra Semiconductors congrats the NICT B5G BRIGHTEN project

Tetra Semiconductors congrats the NICT (The National Institute of Information and Communications Technology) B5G (Beyond 5G) BRIGHTEN project (J012368C00101, J012368C07901) for the invited paper